morning coffee musing: could you make a discrete computer (7400 chips, but the modern versions with fast slew rates and all that) that can run at triple digit MHz?

-

Basically my line of thinking is: these simple chips have been getting faster and faster edges as their dies shrink, which in general causes headaches because people have to deal with high-speed design even if they just needed a lil' inverter. Could you flip that around though, and go hot damn, logic gates with sub-nanosecond rise times, that means they can go real fast if I'm careful about board layout?

-

The bits I'm not sure about are those high-speed design problems though. Even at 100MHz the allowable skew between lines is pretty generous, and with modern CAD tools length matching is ~free anyway. Proper return path design is tricky, but 4-layer boards are affordable these days so should be somewhat possible, for simple computers that don't need too much crossing of signals?

Hobbyist scopes can easily measure a little north of 100MHz now, so you can even look at the signals and debug them.

-

Basically I'm just wondering if it's "just" a really terrible amount of headache to route a board that can do this, or if you hit a fundamental limit even if you get an SI/EMI world expert to do the layout.

-

Aaron Sawdey, Ph.D.replied to Dave Anderson last edited by

@danderson The Cray-1 was built at similar scale of integration using ECL and ran at 80MHz. That suggests to me that it might be possible to do something like this, I think modern CMOS fabrication could give you something faster than that. You'd want to pay a lot of attention to pipelining and signal distribution of course.

-

Extreme Electronicsreplied to Dave Anderson last edited by

@danderson my gut is the track length over a say 200mm PCB would be a good proportion of a wavelength at 100mhz

Termination and especially bidirectional busses would be a nightmare.

-

@acsawdey Right, a big part of the headache is routing global signals like clocks to keep things properly in sync and not violate setup/hold times. And to actually do this you'd need to spend quality time with the datasheets to figure out propagation delays and figure out how long a combinatorial path you can endure. So far it's sounding like a painful puzzle to solve, but possible, maybe.

-

Dave Andersonreplied to Extreme Electronics last edited by

@Extelec you want to worry about the signal rise time more than clock rate, modern ICs are likely to slew faster than the clock rate would suggest.

Two rules of thumb: signals travel at ~15cm/ns, and if you keep the interconnect length under 1/4 of the rise time, it behaves like a lumped element and you can worry less.

So a 500ps rising edge, you'd want to keep trace length under ~1.8cm. Which isn't much, but that's still quite a lot of room to maneuver!

-

@Extelec But yes, if you need to exceed 1.8cm in that example, then ohai welcome to transmission lines, where everything sucks more... But also it's not unknown territory, there are known problems and design techniques to solve them. Serious puzzle to solve in layout, but... possible? I think?...

-

Aaron Sawdey, Ph.D.replied to Dave Anderson last edited by

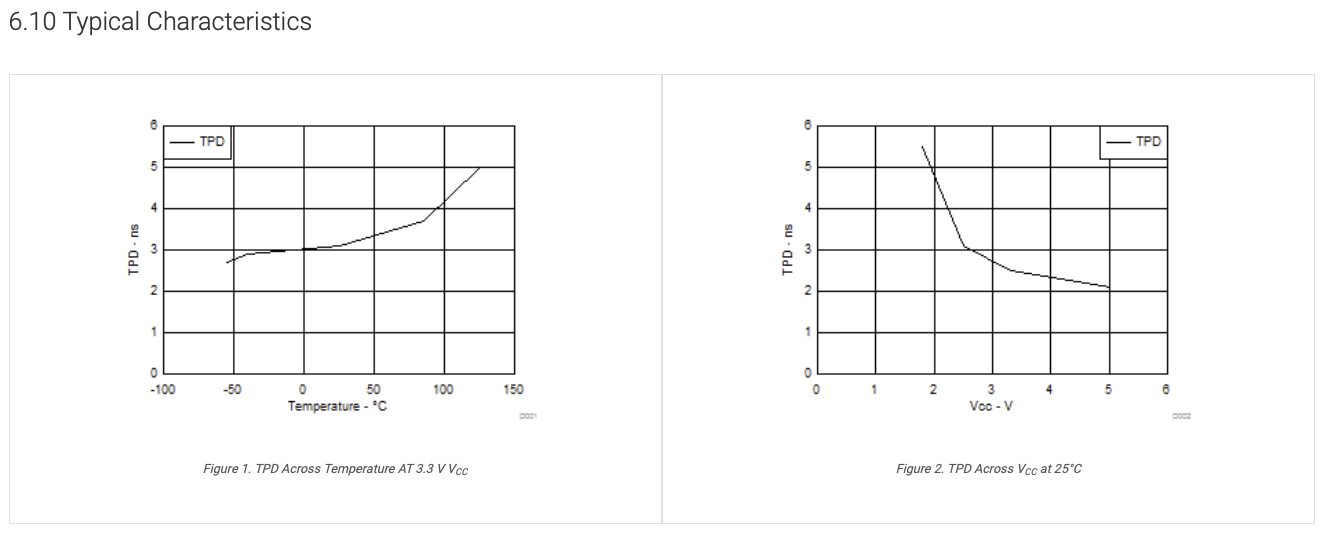

@danderson From the TI data sheet for "SN74LVC1G02 Single 2-Input Positive NOR-Gate"

Suggests to me that running it at 5V and cooling it well could get you in the neighborhood of 2ns, meaning you could get a couple gate delays into a 10ns cycle time. Depends a lot on how much capacitance they are driving. Not sure I picked the fastest gate either.

-

@acsawdey Yeah at a glance on digikey, TI's SN74 chips seem to be the fastest, and under good conditions land around 1-2ns. Assuming it's possible to construct a non-trivial circuit that meets the preconditions, then yeah, that's half a handful of gates per clock at 100MHz, maybe.

Oddly, the datasheet I'm looking at has timing diagrams and test setups, but doesn't actually provide any numbers... It does all the work to name the variables all over the place, then does nothing with them.

-

Extreme Electronicsreplied to Dave Anderson last edited by

@danderson and how do you get around the problems of a bi directional bus? Some form of active termination would be necessary, or some scheme with bi-directional and/or differential line drivers. ?

-

Extreme Electronicsreplied to Dave Anderson last edited by

@danderson Capacitance would be an issue too, you would be fighting the C of the tracks to achieve your rise times, with limited (max) drive current

-

Dave Andersonreplied to Extreme Electronics last edited by

@Extelec Where do you see a bidi line happening? Within the processor my mental sketch only sees single direction lines with a lot of pipelining.

Definitely an issue once you hit any kind of system bus, but I haven't thought that far ahead. Parallel ROMs and RAMs would let you keep everything unidirectional, and I think that plugs in neatly into the cpu pipeline... But I'd have to draw it out in more detail to be sure.

In conclusion, I have no idea

-

Dave Andersonreplied to Extreme Electronics last edited by

@Extelec yeah, glancing at the datasheets for fast logic chips, the quoted fast numbers are caveated quite heavily by how much load capacitance there is. Impedance management in general is where I suspect I don't have enough knowledge to know exactly where the cliff edge is.

-

Extreme Electronicsreplied to Dave Anderson last edited by

@danderson My thought was a "retro" bus, but with differential signals for all the reasons we've stated. (plus x-talk) Terminated at each "end" SCSI style.

complexity is the down side.

-

Dave Andersonreplied to Extreme Electronics last edited by

@Extelec yeah a classic system bus would be the dream, I just straight up don't know enough about high-speed design to know exactly how, I'd have to go learn more.

It's one of those things that's definitely possible since more integrated chips have I/Os like this effortlessly these days. Big question is whether the building blocks are still available as discrete chips, and if the physics tolerate the looser numbers on everything once you de-integrate.

-

@Extelec Well no correction, I know enough to know that multi-device busses on a high speed line where each one grabs the signal partway down the transmission line is Harder(tm) than a simple pair with devices at the ends, but not any of the details of exactly what goes wrong and how it needs to be mitigated.

-

Extreme Electronicsreplied to Dave Anderson last edited by

@danderson Multiple reflections & driving two lines of different lengths & impedances simultaneously, a nightmare of unknowns and variables.

-

Extreme Electronicsreplied to Extreme Electronics last edited by

@danderson And return paths from different parts of the board. ?

-

Dave Andersonreplied to Extreme Electronics last edited by

@Extelec In theory, if the switching rate is fast enough, the return paths will hug the forward signals, so that part at least should be the same design rules as everything else. Reflections off stubs and impedance discontinuities is likely the big killer. I know people design stuff like that all the time, so there must be known techniques for managing it. Or maybe everyone just reaches for a field solver and iterate based on simulation data.